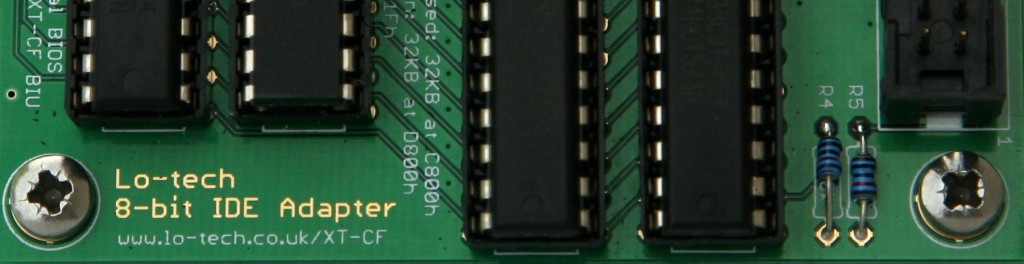

The Lo-tech 8-bit IDE Adapter is a bootable IDE controller for vintage PCs with only 8-bit ISA slots – basically PC/XT class hardware. The adapter is a development of the the Lo-tech ISA CompactFlash Adapter, adding an 8- to 16-bit MUX to make possible the use of normal hard drives, including current SATA drives (via an adapter like this). In this post, I’ll cover how the adapter works.

The Lo-tech 8-bit IDE Adapter is a bootable IDE controller for vintage PCs with only 8-bit ISA slots – basically PC/XT class hardware. The adapter is a development of the the Lo-tech ISA CompactFlash Adapter, adding an 8- to 16-bit MUX to make possible the use of normal hard drives, including current SATA drives (via an adapter like this). In this post, I’ll cover how the adapter works.

16- to 8-bit MUX Design

The main design goal with this adapter is to enable the use of standard, 16-bit drives (‘ATA drives’) with PC/XT class hardware. ATA drives all use both 8- and 16-bit data transfers:

- Port 0 – 16-bit data port. This is where the actual sector data is transferred

- Port 1 to 7 – 8-bit command ports. This is how the drive is told what to do next, like read or write to a sector.

Port IO with 8-bit ISA Cards

In the IBM PC, port IO can also be either 8- or 16-bit, even in XT class hardware with 8-bit ISA slots. Logic in the system known as the bus interface unit (BIU) makes this possible by breaking 16-bit instructions into two consecutive 8-bit bus cycles at consecutive 8-bit port addresses. Hence a single 16-bit port IO is, with 8-bit ISA cards, exactly equivalent to two consecutive 8-bit port IOs:

8-bit ISA cards can still use 16-bit CPU instructions (MSB=most significant byte, LSB=least significant byte)

Note that this applies specifically to hardware in 8-bit ISA slots; when a 16-bit instruction is used with a 16-bit device, all 16-bits are transferred in one bus cycle (and via a single, port 0 in this example). This difference provides both a problem and an opportunity – the ATA specification defines port 0 (only) for (the 16-bit) data transfer, so it just won’t work ‘as-is’ via an 8-bit slot, but secondly the CPU and BIU will already deal with one half of the equation. The 8-bit adapter just needs to break apart 16-bit drive IO into two ISA bus cycles, without the drive noticing.

Port Remapping

Making ports 0 and 1 free for the ATA data register is straightforward – just shift all the command addresses left one bit, a trick already used in the XT-CF line of adapters. With the BIOS code similarly updated, it makes no difference to the drive and this then means address line A0, which distinguishes port 0 from port 1, is free for the adapter to use for something else.

With that in place, 8- or 16-bit port IO can be performed to any of the drives registers, though the ATA specification only calls for 16-bit IO on the data register.

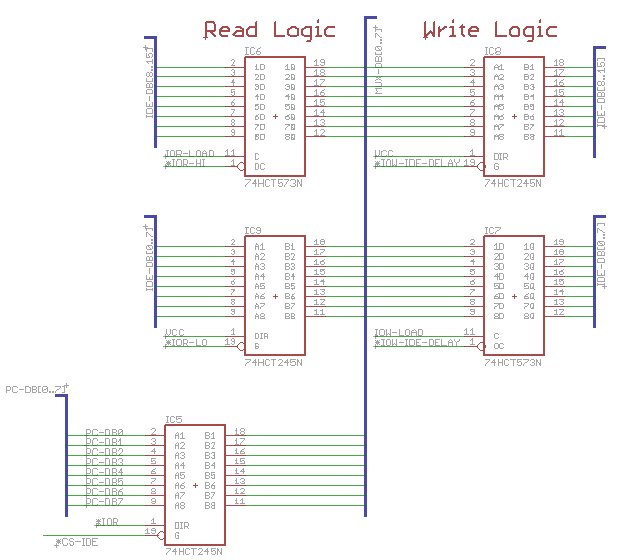

The MUX

The 8- to 16-bit MUX itself uses a separate 74HCT573 and 74HCT245 pair for reads and writes, and another 74HCT245 to link back to the PC data bus. The ‘573 is a latch (like a one-byte memory) providing temporary storage, and the ‘245’s are buffers that can be switched on at will, enabling isolation of certain signals when required.

For reads:

- First bus cycle: a 16-bit word is transferred from the drive. The LSB is presented to the PC data bus and the MSB stored in a latch.

- Second bus cycle: data from the latch is presented to the PC data bus, and the IO signal to the drive suppressed.

For writes:

- First bus cycle: LSB presented on the PC data bus is stored in the latch, and the IO signal to the drive suppressed.

- Second bus cycle: MSB presented on the PC data bus is presented to the drive interface MSB, and data from the latch is presented to the drive LSB.

Interface Timing

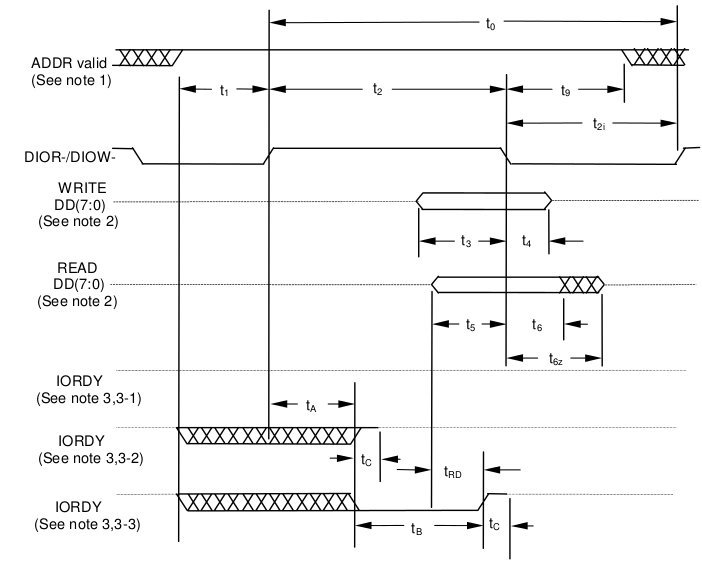

The timing of this process needs some consideration as we need to be sure that data is stored in the appropriate latch before it disappears from the data bus, and secondly that data is presented until just after whatever is receiving it has stored it – this is measured as the data hold time.

For ATA mode 0, the specified data hold times are 5ns for reads (t6), and 30ns for writes (t4).

- For writes, to keep data presented after DIOW line is released at the drive, the latch and buffer outputs are fed from the delayed signal (*IOW-IDE-DELAY in the schematic)

- For reads, the hold time specification of the ‘HCT573 must be observed (9ns). The data being presented by the drive is held beyond the latch time since the drive DIOR line is fed from the delayed signal.

The delays are made by feeding the respective signals through three NOT gates (the control logic already inverts it once) in IC14. The delay can be controlled by the component choice (~15ns with SN74LS04N, or about 25ns with SN74HCT04N). Without the delay lines, for example in the case of a write the latch output would be turned off just as the drive latches the data because of zero hold time – the data may or may not still be valid as the drive stores the data.

PCB Errata

In the first version of this board, the write latch load signal is masked unless the request is port 0, which works for the data register but also means no commands can be issued to the drive! Instead, the signal should be masked only when the request is port 1, which can be fixed by modifying the 74HCT02N that will be fitted as IC11 – more details to follow in a build post.

Lo-tech is in no way associated with the sellers of products on other sites linked to on this page (which are provided to provide an example of the types of products available).

So when will u release this 8 bit ide mux?

Hi Sean, full kits will be available in the next few weeks!