Tandy helpfully included an expansion slot in their 1400 series of laptops, and in places there is reference to an expansion box, but it seems it never made it to market. The later 1400FD and 1400HD models retained the expansion slot and added a second (slightly different) slot for an MFM HDD controller, as implemented in the 1400HD.

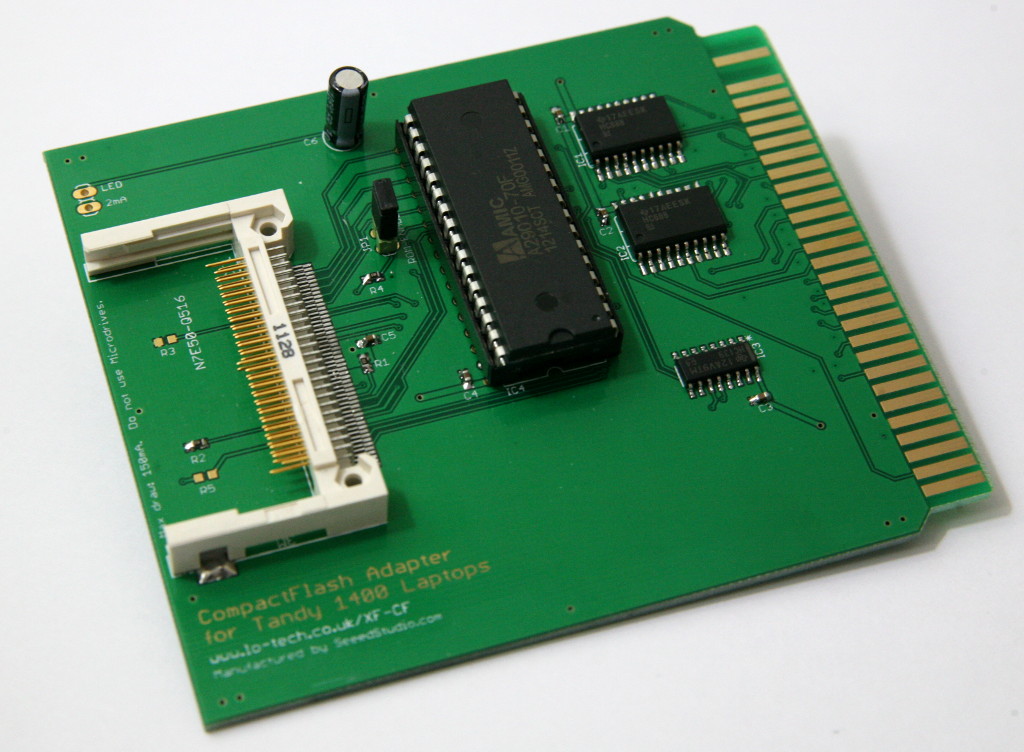

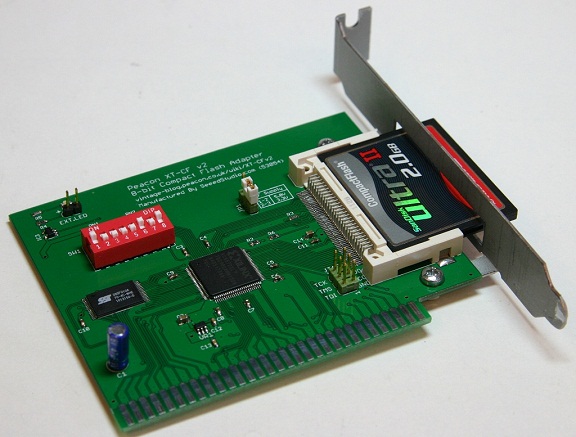

The expansion slot is basically an 8-bit ISA slot, but with a different pinout and a few differences, in a custom card form factor to fit in the machine. Power budget is also limited to 200mA, according to the service manual. Fortunately, Tandy documentation provides everything needed to create a card – so here is what I believe to be the first ever expansion card for Tandy 1400 Series laptops (only about 20 years late):

Expansion Card Design

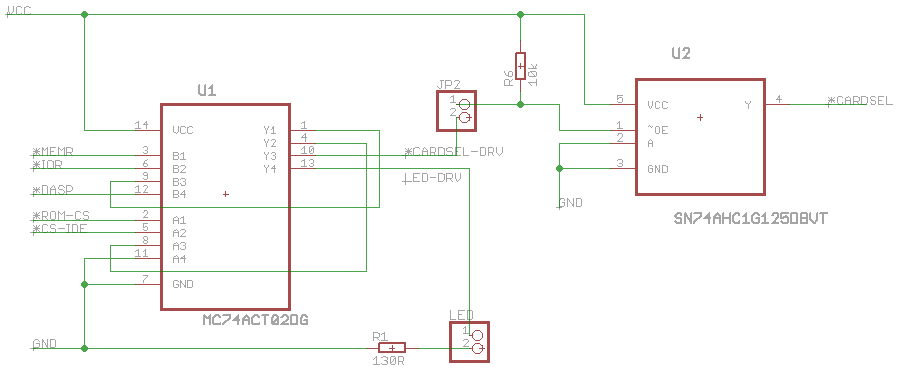

Based on the information available in the Tandy technical reference, I’ve created a wiki page detailing everything about the expansion slots. Some of the Tandy documentation is contradictory, but my wiki is based on what is now a proven design. I’ve also included an Eagle layout for the PCB (restricted to a 100 x 100mm footprint, to enable low-cost manufacture by SeeedStudio).

XT-CF

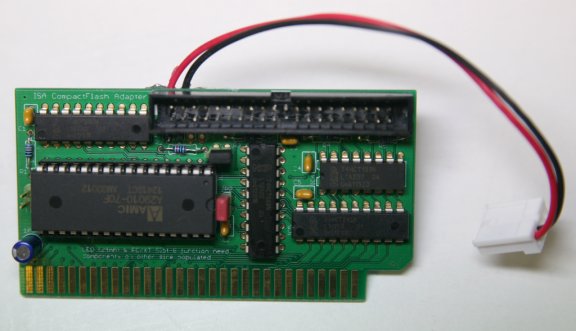

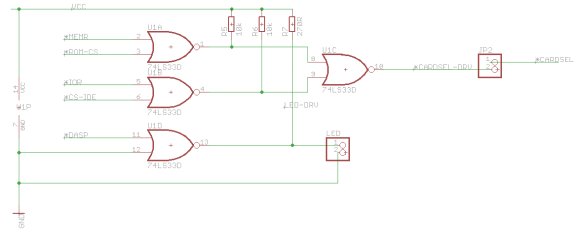

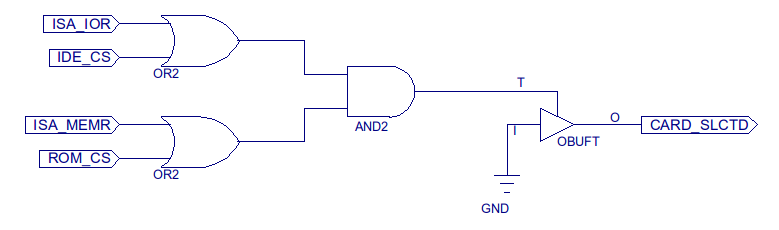

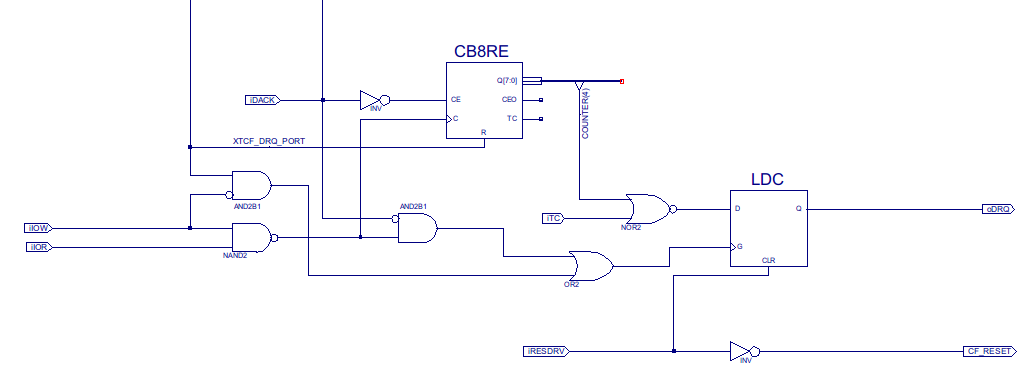

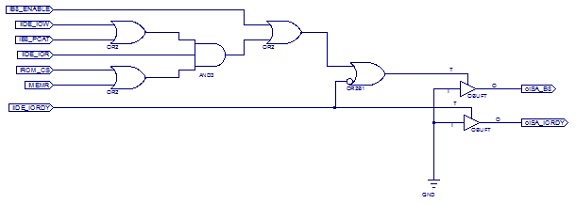

My XT-CF cards provide hard disk functionality to PC/XT and PC/AT class machines based on CompactFlash (or microdrives), and for the Tandy 1400 the design needs just four ICs – a flash ROM, two 74688 address decoders and a 74139 decoder. Being XT-CF compatible, the design is fully supported by the XTIDE Universal BIOS (from build r554).

BIOS Initialisation

I built this board a while back, and although BIOS flashing went OK the machine didn’t want to initialise the XTIDE Universal BIOS. The BIOS was clearly detecting the option ROM as the floppy seek test was performed on only the first floppy with it present (the BIOS assuming that an HDD would be installed in place of the second floppy, exactly as the 1400HD was shipped), but the BIOS initialisation messages never appeared.

This has had me stumped and the board simply sat on the side since. But recently XTIDE Universal BIOS project lead Tomi posted a code update (in r552):

XTIDE Universal BIOS can now be initialized if non-standard main BIOS does not call INT 19h or if INT 19h handler is replaced by some other BIOS.

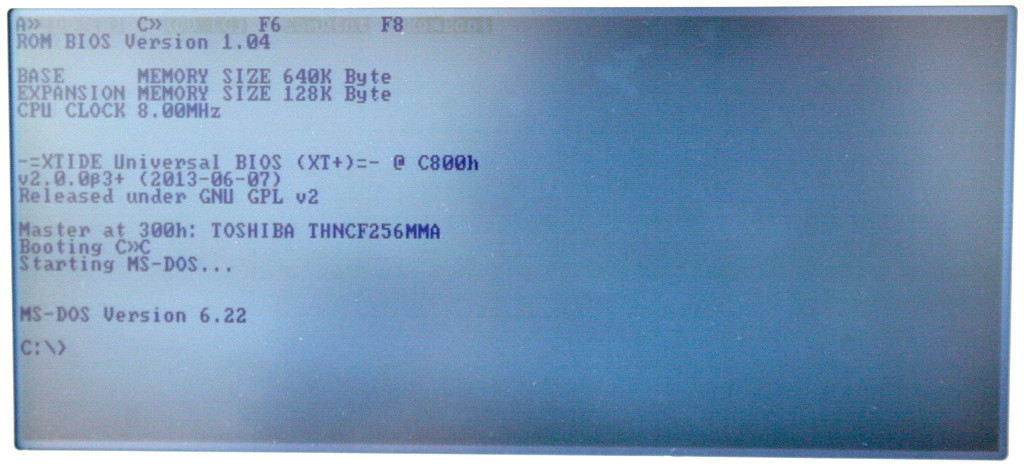

And sure enough, the BIOS fired into life and the machine booted (and yes, the SuperTwist LCD screen really does look this bad):

The solution isn’t quite perfect – the fixed disk is inaccessible when restarted via CTRL-ALT-DELETE, but since boot time on this machine is identical for both soft boot and cold boot, this is just something that we need to live with for now.

1400LT, 1400FD and 1400HD

For 1400FD systems at least with BIOS 1.04, the system BIOS assumes the second floppy isn’t installed when the XT-CF option ROM is present (this may also affect 1400LT systems). For now this is a limitation, but with 32KB of flash ROM available it should be possible to resolve it by adding a floppy BIOS to the card.

For 1400HD machines, the MFM controller must be removed since both cards have their BIOS at C800h (upper memory space is somewhat limited in the 1400 series as Tandy included RAM in the upper memory area for use as a RAM disk).

Performance

Using the ‘XTplus’ XTIDE Universal BIOS build (thanks to the V20 CPU), DOS throughput (as measured with my own test utility) is at least 550KB/s. Due to the 8-bit data bus and V20 microcode optimisations, there is no performance difference between standard 8-bit PIO and BIU offload modes (as set with XTCFMODE), although both modes are supported.

Availability

ENIG PCBs (gold plated) are available now through the shop page.

Components will also be needed from your local electronics outlet such as Farnell, Mouser or Digikey – full Bill of Materials in the wiki. There is no bracket needed, since the card slides into the expansion slot guides within the system chassis, and the fit into the slot is tight enough not to need and further support.